10. 放射光源加速器の入射パルス電磁石電源

高エネルギー加速器研究機構 篠 原 智 史

# 目 次

# 放射光源加速器の入射パルス電磁石電源

| 1 | はじめに                                                         | 10-  | 1  |

|---|--------------------------------------------------------------|------|----|

| 2 | 電子蓄積型放射光加速器における入射システム                                        |      |    |

|   | 2.1 加速器入射構成の概要                                               | 10-  | 1  |

|   | 2.2 バンプ軌道を用いたビーム入射方式                                         | 10-  | 2  |

|   | 2.3 入射パルス電磁石に要求されること                                         | 10-2 | 2  |

| 3 | 入射パルス電磁石電源の基本概念                                              |      |    |

|   | 3.1 キッカーの種類について                                              | 10-3 | 3  |

|   | 3.2 パルス電源の種類と特徴                                              | 10-3 | 3  |

|   | 3.3 パルス電流の定格評価                                               | 10-  | 4  |

| 4 | パルス電源基本設計                                                    |      |    |

|   | 4.1 パルス電源の基本構成と動作概要                                          | 10-  | 5  |

|   | 4.2 理想回路のパルス出力電流                                             | 10-6 | 6  |

|   | 4.3 回路浮遊成分がある場合のパルス出力                                        | 10-  | 7  |

|   | 4.4 充電部の回路動作                                                 | 10-9 | 9  |

|   | 4.5 回路パラメータの設定                                               | 10-1 | 0  |

|   | 4.6 スナバ回路によるノイズの抑制                                           | 10-1 | 1  |

| 5 | スイッチ部の進化と半導体スイッチ                                             | 10-1 | .1 |

|   | 5.1 高電圧・大電流スイッチとその候補デバイス概要                                   | 10-1 | 2  |

|   | 5.2 SiC パワー半導体デバイスとその構造 ···································· | 10-1 | .3 |

|   | 5.3 半導体スイッチの基本動作                                             | 10-1 | 4  |

|   | 5.4 設計時の注意事項                                                 | 10-1 | .4 |

| 6 | 半導体パルス電源開発例                                                  | 10-1 | 6  |

| 7 | まとめ                                                          | 10-1 | 7  |

| 参 |                                                              | 10-1 | 7  |

# 放射光源加速器の入射パルス 電磁石電源

## 1 はじめに

電子蓄積リング放射光加速器の運転には、多種多様な電磁石が必要であり、これらを駆動する電源系は、加速器運転の根幹をなす技術要素の一つである。一般に電磁石といえば、まず蓄積ビームの軌道を決定するための偏向電磁石や四極・六極電磁石など、静的な直流電流を用いる装置に触れることが多い。一方、ビームを蓄積リングに入射する際には、動的なパルス電流を用いる電磁石と、それを駆動する専用の電源が必要となるが、それらに関する情報に触れる機会は比較的限られている。そこで、本稿ではDC電源とは対照的なパルス電源、特に放射光源加速器の入射部に用いられるパルス電磁石用の電源に焦点を当てる。

パルス電磁石は、電子ビームを蓄積リングへ入射する際に不可欠な要素であり、その駆動には高速かつ高電力のパルス電源が要求される。本稿ではまず、なぜ入射時にパルス電磁石が必要とされるのか、その背景と、そこから導かれるパルス電源の定格条件について述べる。次に、これらの条件を満たすための電源回路の構成について、簡潔な回路例を通じて電源に必要なパラメータを定量的に検討する。続いて、パルス電源の中核であるスイッチングデバイスについて、近年応用が進んでいるパワー半導体、特にMOSFETやIGBTを中心に、それらの構造、動作原理、駆動方法、および設計における留意点を開発例とともに解説する。

パルス電源の設計では、回路構成や素子選定 のみならず、熱設計、ノイズ対策、高電圧絶縁 構造など、多岐にわたる検討要素が存在する。 実際にパルス電源を設計・製作しようとすると、 数多くのノウハウが必要となる場面に直面し悩 まされることも多いが、本稿で少なくともパル ス電源に関する基礎的な理解と、実装・応用に 向けた設計の出発点となる知見を提供できれば 幸いである。

# 2 電子蓄積型放射光加速器における入射 システム

この章では、電子蓄積型放射光加速器における入射システムの概要とそこでパルス電源に求められる定格について考える。入射システムの詳細については前講義(満田氏による講義内容)を参照されたい。

## 2.1 加速器入射構成の概要

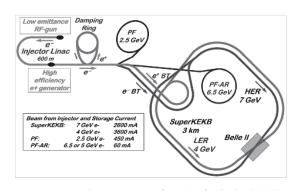

電子蓄積型放射光加速器において、蓄積リン グのエネルギーまで加速された電子ビームを 蓄積リングに合流させる操作をビーム入射と 呼ぶ。こうした加速器の入射構成には、主に次 の二つの方式がある。一つは、線形加速器で電 子ビームを直接蓄積リングのエネルギー(一 般に数 GeV) まで加速し、そのまま蓄積リン グへ入射する方式、もう一つは、線形加速器で 100 MeV オーダーまで加速した後、さらにブー スターリングによって蓄積リングエネルギーま で加速し、入射する方式である。例えば、KEK の電子蓄積型放射光加速器 PF および PF-AR は 前者に該当し、線形加速器でリングのエネル ギーまで加速して入射する。PF へ入射する場合 は 2.5 GeV、PF-AR に入射する場合は 5 GeV も しくは 6.5 GeV まで線形加速器にて加速してい る (図 1)。 世界的には、放射光源加速器への 入射には、専用の線形加速器やブースターリン グを用いる方式が主流である。これに対し KEK では、一本の線形加速器によって、PF、PF-AR、 SuperKEKB など、複数の加速器にビームを供 給する方式となっている。このような構成は世

図 1: KEK 加速器の全体の概要図 [1]

界的にも珍しく、大規模な素粒子実験と放射光 実験の両方を、単一の線形加速器で賄っている 点において、効率的な加速器運用形態の一例と もいえる。

## 2.2 バンプ軌道を用いたビーム入射方式

電子蓄積リングにおけるビーム入射には、バンプ軌道を用いる方式が一般的に採用されている。本節ではこのバンプ軌道を用いた入射方法について説明する。

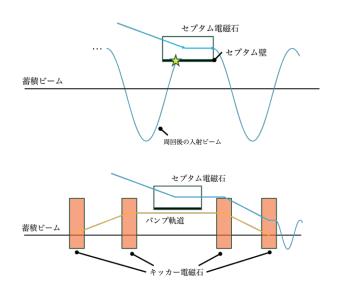

ビーム入射では、入射路から導かれた電子 ビームをセプタム電磁石とよぶ電磁石によって 蓄積リングの軌道に沿うよう調整する。セプタ ム電磁石は、蓄積ビームに磁場の影響を与えな いよう、セプタム壁と呼ばれる薄い遮蔽板に よって磁場領域を区画した構造をもつ。このと き、単にセプタム電磁石からのビームを導入す るだけでは、入射ビームはセプタム壁の外側か ら蓄積ビームの理想軌道を中心にベータトロン 振動を開始し、周回後にセプタム壁へ衝突して 失われてしまう (図 2 上)。この問題を回避す るため、図2下に示すように、キッカー電磁石 によってバンプ軌道を形成し、蓄積ビームを入 射ビームに近づける。これにより、入射ビーム の初期振幅はバンプ軌道の分だけ抑制される。 その後、バンプ軌道を閉じることで、蓄積ビー ムは元の軌道に復帰し、入射ビームも振幅が抑 えられた状態で振動を開始する。こうして入射 ビームはセプタム壁に衝突せずにリングを周回 し、放射減衰により振幅を減少していき、最終 的に蓄積ビームと合流する。

このバンプ軌道は入射時のみに形成される必要があることに注意する。バンプを立てたままでは、入射ビームが軌道に沿って振動を続け、再びセプタム壁に衝突してしまうためである。したがって、キッカー電磁石は入射タイミングに合わせてオンデマンドに駆動されなければならない。

# 2.3 入射パルス電磁石に要求されること

バンプ軌道によるビーム入射においては、 キッカー電磁石およびセプタム電磁石に特定の

図 2: バンプ軌道による入射システムの概要。バンプを立てない場合 (上図) とバンプを立てた場合 (下図)。

蹴り角やパルス磁場波形が要求される。以下では、それぞれに必要とされる蹴り角とパルス幅について考えてみる。

まずキッカー電磁石に必要な蹴り角について考える。蓄積リング入射部の長さは、キッカー電磁石 4 台とセプタム電磁石などが配置されており、施設の規模や設計により異なるが、おおよそ 5-10 m 程度である。例として、キッカー電磁石を 3 m 間隔で配置し、10 mm のバンプを形成する場合を考えると、必要な蹴り角は3.3 mrad (=10 mm/3 m) と見積もられる。この例のように、キッカー電磁石には通常、数 mradの蹴り角を発生させる磁場が求められる。蹴り角の精度も重要であり、たとえば0.1%の誤差があると、上の例では3 m 先で約10  $\mu$ m の位置ずれが生じる。次世代放射光源加速器ではこうした誤差も問題となるため、パルス磁場の出力安定性には0.1%程度が要求される。

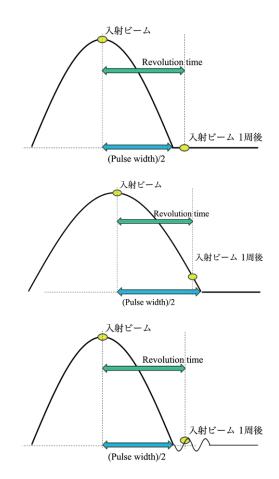

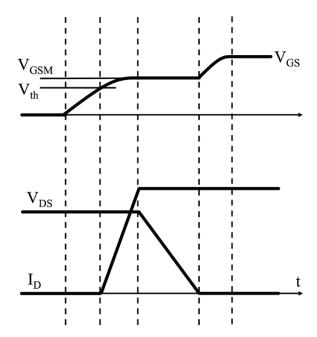

またキッカー電磁石の磁場パルス幅は、電子ビームのリング周回時間(revolution time)の2 倍以下という制約が課される。図3 に示すようにパルス幅が長すぎると、入射ビームが一周後に再びキックを受けるおそれがあり、軌道が乱れるとともに入射調整の複雑化を招く。加速器の周長は施設によって異なるが、たとえ

ば PF では 187 m であり、これを光速で除した revolution time は約 624 ns である。したがって、PF の例ではキッカー電磁石のパルス幅はその 2 倍、すなわち  $1.2~\mu s$  以下に抑える必要がある。パルス出力後のノイズも気にする必要があり、図 3 下図のようなノイズが存在する場合にも入射ビームは影響を受けてしまう。後述するが、短パルス出力を要求されるパルス電源にはこうした後段のリンギングノイズがのりやすいため注意が必要である。

セプタム電磁石に関しては、キッカー電磁石 よりも大きな蹴り角が必要となる。これは入射 ビームが通る入射路と蓄積リングを空間的に十 分切り離すためである。たとえば、1.5 m 先の 距離で 15 cm リングから離したい場合には、 100 mrad の蹴り角が必要である。セプタム電 磁石は蓄積リングへの漏洩磁場を最小限に抑え る必要があり、遮蔽効果を高める渦電流の発生 を利用したパルス磁場による駆動が適している。 この理由からセプタム電磁石も一般にパルス電 磁石として設計するが、入射路ではビームが一 度しか通過せず、また入射操作そのものも数 Hz の低繰り返しで行われるため、キッカー電磁石 と比べてパルス幅に対する要求は緩い。そのた め、セプタム電磁石のパルス幅は  $100~\mu s$  オー ダーと比較的長く設定することが可能である。

## 3 入射パルス電磁石電源の基本概念

本章ではパルス電磁石を駆動するためのパルス電源について、パルス発生方法の原理や種類を述べる。また前節で示した所定の蹴り角を得るために必要な電流量について考察する。

### 3.1 キッカーの種類について

ここまで入射用のキッカーは電磁石であることを念頭においていたが、電場型のキッカーについても一度考察してみる。電子に働くローレンツ力は

$$F = qE + qvB \tag{3-1}$$

であるが、電子蓄積リングの入射においては、その時点で電子はほとんど光速まで加速されている。つまり電子の速度 v はほとんど

図 3: キッカー電磁石の磁場波形と入射ビームの 関係。上図ではパルス幅の条件を満たしている が、中段の図ではパルス幅が長く、入射ビーム が複数回蹴られてしまう。下図もノイズにより 入射ビームが複数回蹴られてしまう。

$v=3\times 10^8$  m/s である。例えば磁場 B=0.3 T と同等の力を電場で電子に与えようとする場合には、電場 E は 1 GV/m 程度必要であることが分かるが、これは普通困難である。こうした理由により入射用のキッカーでは通常電場型ではなく磁場型で設計する。

# 3.2 パルス電源の種類と特徴

前節で述べたように、キッカーでは磁場型が 用いられるため、負荷はインダクタンス負荷(L負荷)となる。この L 負荷に対して所定のパルス電流を供給するには、主に以下の二つの方式 が採用されている。一つは、コンデンサに蓄え たエネルギーを集中定数回路を介して負荷へ一 気にパルス的に放出する方式、もう一つは、同軸ケーブル等の分布定数素子を用いてパルスを 形成し負荷にパルス電流を供給する方式である。

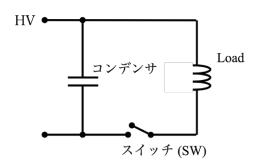

集中定数回路型 (LC 共振方式): 回路の基本構成は、図 4 に示すように、コンデンサに電圧を印加して  $\frac{1}{2}CV^2$  のエネルギーを蓄積し、それを L 負荷に対して  $\frac{1}{2}LI^2$  の形で変換する。負荷電流波形は、コンデンサとインダクタンスとの間で LC 共振が生じるため、以下のような正弦波となる:

$$i(t) = V\sqrt{\frac{C}{L}}\sin\left(\frac{t}{\sqrt{LC}}\right)$$

(3-2)

LC 共振回路の方式は回路構成をシンプルにできるメリットがある一方で、配線のインダクタンス低減化や回路を集中定数として扱うために伝送線路は出力パルスの波長より十分短くする必要がある(例えば必要パルス幅が  $\mu$ s オーダーの場合、波長は数 100 m 程度である。)そのためパルス電源は加速器トンネル内のキッカー電磁石近傍に設置することが望ましく、その際には装置の小型化や放射線耐性にも配慮する必要がある。

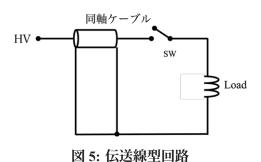

分布定数回路型(PFN / PFL 方式): 分布定数回路型では図 5 に示すようパルス整形回路として PFN (pulse forming network) または PFL (pulse forming line) を用いる。例えば同軸ケーブルやストリップラインのような分布定数をもつ伝送線路が使用される。特性インピーダンスを  $z_0$  とすると電流は

$$i(t) = \frac{V}{z_0} \left( 1 - \exp(-\frac{z_0}{L}) \right)$$

(3-3)

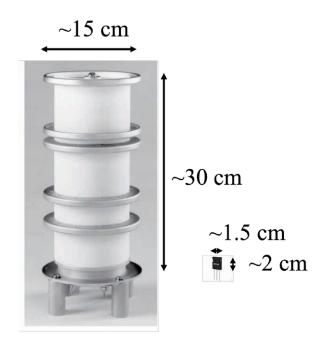

で立ち上がる [2]。この方式のメリットは、PFL として同軸ケーブルを使用できるため入手性が良いこと、また、同軸ケーブルは長さによって特性が変わらないため、ケーブルを長くして電源を加速器トンネル外に設置できる点である。一方でデメリットとしては、大量のケーブルが必要になり電源が大型化し設置場所を圧迫する。図 6 は PF キッカー電磁石 1 台分の電源 PFL 部とパルス生成部である。人よりもかなり大きいキッカー電源がこの図の他に 3 台分ありスペー

スの占有率は大きい。近年の放射光加速器では 性能を落とさずにできるたけ施設を小型化する ことが命題にもなっている。後述のパルス電源 の半導体化と合わせた集中定数方式回路への切 り替えも近年のトレンドになっている[3]。

図 4: LC 共振回路

## 3.3 パルス電流の定格評価

パルスキッカー電磁石はインダクタンス負荷であり、パルス電源で生成したパルス電流をインダクタへ供給することで、パルス磁場を生成する。本節では、そのパルス電源に必要な電流定格について述べ、パラメータ例をもとに定格の概算を行う。

電磁石がビームに与える蹴り角を $\theta$ 、磁石長を $\ell$ 、ビーム軌道の曲率半径を $\rho$ とするとそれらの関係は、以下のように表される。

$$\theta = \frac{\ell}{\rho} \tag{3-4}$$

一方、ローレンツ力に基づく電子の運動量p [GeV/c]、磁場B [T]、および曲率半径 $\rho$  [m] の関係は、

$$p = 0.3B\rho \tag{3-5}$$

図 6: PF 伝送線型キッカー電磁石電源の一部

で与えられる。これらを組み合わせることで、 磁場と磁石長  $\ell$  の積は次のように導出される。

$$B\ell = \frac{p\theta}{0.3} \tag{3-6}$$

次に、磁場Bをコイルに流す電流Iと巻き数n、およびギャップ高さhから表すと、

$$B = \frac{\mu_0 nI}{h} \tag{3-7}$$

である ( $\mu_0$  は真空の透磁率)。式 (3-6) および式 (3-7) を組み合わせることで、必要な nI 積、すなわち電流と巻き数の積が導かれ、必要な電流値を決める重要な指標が得られる。電磁石のインダクタンス L は磁極間隔の面積 S を用いて以下のように表せる。

$$L = \frac{\mu_0}{h} n^2 S \tag{3-8}$$

キッカー電磁石に必要な電流値を考える例として、 $2.5~{\rm GeV}$  の蓄積リングにおいて蹴り角 $\theta=4.0~{\rm mrad}$ 、磁石長 $\ell=0.40~{\rm m}$ 、ギャップ高さ $h=60~{\rm mm}$ 、ギャップ幅 170  ${\rm mm}$  の場合を考える。このとき、式 (3-6) より必要な  $B\ell$  積は:

$$B\ell = \frac{2.5 \times 4.0 \times 10^{-3}}{0.3} \approx 0.03 \text{ T} \cdot \text{m}$$

(3-9)

したがって、 $B = B\ell/\ell = 0.033/0.4 \approx 0.08$  T である。式 (3-7) より、必要な nI 積は:

$$nI = \frac{Bh}{\mu_0} = \frac{0.083 \times 0.060}{1.26 \times 10^{-6}} \approx 4.0 \times 10^3 \text{ A·turn}$$

(3-10)

以上より、必要な電流はおよそ 4 kA·turn である。このときインダクタンス値は式 (3-8) より  $1.4 \mu H$  と計算できる。

パルス電磁石においては、DC 電磁石とは異なりコイル巻き数は1回または2回巻き (n=1,2)程度である。これは巻き数を増やしすぎるとキッカーが大きくなって入射部に入れづらくなったり、インダクタンスが増加すると高速動作設計が難しくなるためである。また巻き数を中途半端に増やすとコイル間の層間絶縁も課題になるため1,2回巻が設計としては妥当である。このため入射キッカー用パルス電源にはkA 級のパルス電流を供給することが求められる。

# 4 パルス電源基本設計

前章で述べたように、パルス電源と一口にいっても様々な構成が存在し、設計思想も用途に応じて異なる。そこで本節では、直観的にも理解しやすい集中定数型のパルス電源を例に、その基本的な設計要素と動作原理について述べる。

# 4.1 パルス電源の基本構成と動作概要

集中定数型パルス電源は、コンデンサに蓄積 したエネルギーを瞬時に放出することでパルス 電流を得る方式である。以下では、この方式に おける基本構成と動作の概要を述べ、後の節に て定量的な議論を行う。

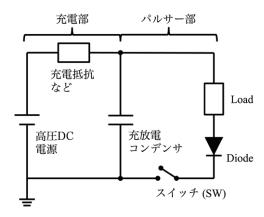

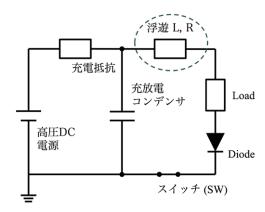

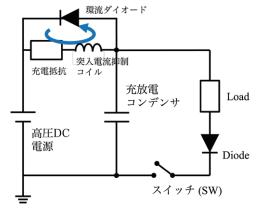

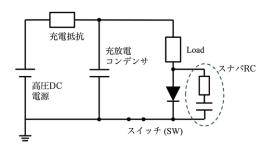

一般にパルス電源は、大きく分けてエネルギーを蓄積する「充電部」と、蓄積されたエネルギーを負荷に供給する「パルサー部」から構成される。図7にその代表的な構成例を示す。

充電部は、主にコンデンサへのエネルギー供給を担う回路であり、構成要素としてまず充電用のDC電源が必要となる。後述するが、kA級の電流出力を得るには10kVオーダーの非常に高い充電電圧が必要となるため高圧DC電源が

図 7: パルス電源の基本構成: 充電部とパルサー部

必要である。また充電部には、充電速度を調整するとともに、スイッチ動作時の回路への過渡的影響を抑制するため、充電経路には抵抗やインダクタなどの素子が挿入される。

パルサー部の構成には、充放電用コンデンサ、整流用ダイオード、スイッチ、およびインダクタンス負荷が含まれる。このうちスイッチは、パルス電源における中核的役割を果たし、高電圧・大電流を高精度に制御する性能が要求される。たとえば、スイッチのタイミングにジッターが生じると、出力波形のピーク位置が変動し、ビームへの蹴り角の再現性が低下する。スイッチの構造や駆動技術については後の章で詳述し、本節では理想スイッチとしての振る舞いを仮定する。

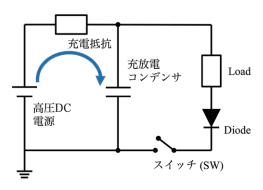

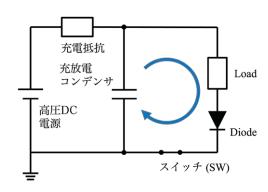

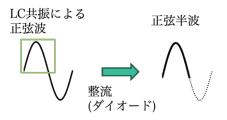

次にパルス電源のパルス出力動作について述べる。まず図 8 に示すようなスイッチがオフの状態を考える。このときパルサー部には電流は流れないので、高圧 DC 電源から充放電コンデンサへと充電される。充電が完了したところでスイッチをオンにするとパルサー部ではコンデンサは図 9 の矢印の向きに放電する。放電電流の波形はコンデンサとインダクタンス負荷による LC 共振を起こすため正弦波となる。この正弦波をダイオードによって整流することで正弦半波を生成するパルス電源となる(図 10)。

図 8: SW オフ時の動作

図 9: SW オン時の動作

#### 4.2 理想回路のパルス出力電流

パルス電源から出力される電流波形について、本節では定量的に解説する。まずは、回路の浮遊成分が存在しない理想的な *LC* 共振回路を仮定し、その動作を考察する。

あらかじめコンデンサが電圧  $V_0$  で充電されており、時間 t=0 において理想スイッチがオンとなる状況を考える(図 9)。コンデンサの容量をC、負荷インダクタンスを L とする。ここでは、インダクタンス負荷に流れる放電電流に着目するため、図 9 に示す矢印の方向を電流の正方向

図 10: 正弦半波出力の概要図

として定義する。このとき、コンデンサの電荷 q(t) に対してキルヒホッフの法則を適用すると、以下の微分方程式が得られる。

$$\frac{q(t)}{C} + L\frac{di(t)}{dt} = 0 {4-1}$$

ここで、i = dq/dt の関係から整理すると、

$$\frac{1}{LC}q(t) + \frac{d^2q(t)}{dt^2} = 0 {(4-2)}$$

と 2 階の微分方程式で表すことができ、図では 放電電流の向きを正としているから初期条件  $q(0) = -CV_0, i(t) = 0$  に注意すると、

$$q(t) = -CV_0 \cos \frac{t}{\sqrt{LC}} \tag{4-3}$$

$$i(t) = V_0 \sqrt{\frac{C}{L}} \sin \frac{t}{\sqrt{LC}}$$

(4-4)

インダクタとコンデンサにかかる電圧をそれぞれ $V_L$ ,  $V_C$  とすると、

$$V_L(t) = -V_C(t) = -\frac{q(t)}{C} = \frac{V_0}{L} \cos \frac{t}{\sqrt{LC}}$$

(4-5)

である。電流波形は正弦波となり、電圧波形は 電流と位相が 90 度ずれた動きをとることにな る。負荷に流れる電流の最大値 (ピーク電流値) は

$$I_{peak} = V_0 \sqrt{\frac{C}{L}}$$

(4-6)

周期は

$$T = 2\pi\sqrt{LC} \tag{4-7}$$

である。このままでは正弦波のままであるから、ダイオードによって整流することでダイオード順方向に流れる正弦半波を生成することができる。その後スイッチを再びオフ状態にすることで、コンデンサへの充電が始まり、定常状態へと至る。このスイッチング動作を繰り返すことで、ダイオード順方向に流れる正弦半波パルス電流を繰り返し生成する。正弦半波のパルス幅w はダイオードにより整流するため LC 共振周期の半分であり、

$$w = \pi \sqrt{LC} \tag{4-8}$$

である。ピーク電流値 (式 (4-6)) はパルス幅 w を使って次のようにも書ける。

$$I_{peak} = \frac{w}{\pi} \frac{V_0}{L} \tag{4-9}$$

電源運用上はコンデンサ容量よりもパルス幅が わかることの方も多いため、こちらの表式も データを当たる際には便利である。

# 4.3 回路浮遊成分がある場合のパルス出力

前節では、回路浮遊成分が存在しない理想的な *LC* 共振回路に基づいてパルス電流を導出した。本節では、より実際に近い構成として、図 11 のような回路内に浮遊成分が存在する場合について検討する。

回路浮遊成分には、電源配線ループによる浮遊インダクタンス、素子の寄生抵抗や寄生容量などが含まれる。本節の回路方式は集中定数回路を仮定しているので電源回路のインダクタンス L や抵抗 R については

$$L = L_{\text{load}} + L_{\text{strav}} \tag{4-10}$$

$$R = R_{\text{parasitic}}$$

(4-11)

と合成して考えることができる。ここで  $L_{\text{load (stray)}}, R_{\text{parasitic}}$  はそれぞれ負荷インダクタ ンス(浮遊インダクタンス)と寄生抵抗の値で ある。まず浮遊インダクタンスについて、原因 となるのは電源回路のループがあげられる。例 えば直径 50 cm のワンターンコイルがもつイン ダクタンスは 2 μΗ 程度ある。通常の電子回路 からすると大きなループに感じられるかもしれ ないが、パルスキッカー電源では数十kVの高電 圧を扱うため、絶縁距離を確保する必要があり、 スイッチイングデバイスひとつでも 20-30 cm スケールの構造となる場合が多い。そのため、 意識的に設計しない限り、この程度の浮遊イン ダクタンスは容易に回路中に現れる。これは、 3.3 節で取り上げたキッカー電磁石のインダク タンス (たとえば 1.4  $\mu$ H) と同程度であり、全 く無視できない影響を与える。また寄生抵抗に ついても理想的な LC 共振では考えなかったパ ラメータのため、本節では影響を考慮する。一

方で、寄生容量については後の節にて紹介するが、充放電コンデンサの容量は  $100\,\mathrm{nF}$  程度と比較的大きく、回路寄生容量は構成にもよるがせいぜい  $100\,\mathrm{pF}$  程度なので影響は小さいとして考える。

以上の仮定により、回路は LCR 回路になる。 キルヒホッフの法則により、以下の式が成り 立つ。

$$\frac{q(t)}{C} + L\frac{di(t)}{dt} + Ri(t) = 0 \tag{4-12}$$

両片を時間微分をして整理すると、

$$\frac{d^{2}i(t)}{dt^{2}} + \frac{R}{L}\frac{di(t)}{dt} + \frac{i}{LC} = 0$$

(4-13)

ここで解を

$$i(t) = e^{\lambda t} \tag{4-14}$$

とおくと、

$$e^{\lambda t} \left( \lambda^2 + \frac{R}{L} \lambda + \frac{1}{LC} \right) = 0 \tag{4-15}$$

である。 $e^{\lambda t} \neq 0$  であるから、

$$\lambda^2 + \frac{R}{L}\lambda + \frac{1}{LC} = 0 \tag{4-16}$$

を得る。この特性方程式の解は、

$$\lambda = -\frac{R}{2L} \pm \sqrt{\left(\frac{R}{2L}\right)^2 - \frac{1}{LC}} \tag{4-17}$$

従って i(t) の一般解は  $\alpha = \frac{R}{2L}$ ,  $\omega_0 = \frac{1}{\sqrt{LC}}$  とおくと、

$$i(t) = A_0 e^{\left(-\alpha + \sqrt{\alpha^2 - \omega_0^2}\right)t} + A_1 e^{\left(-\alpha - \sqrt{\alpha^2 - \omega_0^2}\right)t}$$

$$= e^{-\alpha t} \left(A_0 e^{\sqrt{\alpha^2 - \omega_0^2}t} + A_1 e^{-\sqrt{\alpha^2 - \omega_0^2}t}\right)$$

(4-18)

である。i(t) = 0 より、 $A_0 + A_1 = 0$  であり、また

$$V_0 = L \left. \frac{di}{dt} \right|_{t=0} = 2L\sqrt{\alpha^2 - \omega_0^2} A_0$$

(4-19)

より、

$$A_0 = -A_1 = \frac{V_0}{2L\sqrt{\alpha^2 - \omega_0^2}}$$

(4-20)

である。一般解は  $\alpha^2 - \omega_0^2$  の符号でその挙動を かえる。 $\alpha^2 - \omega_0^2 < 0$  の場合は

$$i(t) = \frac{V_0}{L\sqrt{\omega_0^2 - \alpha^2}} e^{-\alpha t} \sin \sqrt{\omega_0^2 - \alpha^2} t$$

(4-21)

と求まる。これは時定数  $\alpha$  で減衰する減衰振動を表している。同様にして他の場合についても計算すると、 $\alpha^2-\omega_0^2=0$  の場合は

$$i(t) = \frac{V}{L} t e^{-\alpha t} \tag{4-22}$$

$\alpha^2 - \omega_0^2 < 0$  の場合は

$$i(t) = \frac{V}{L\sqrt{\alpha^2 - \omega_0^2}} e^{-\alpha t} \sinh\sqrt{\alpha^2 - \omega_0^2} t \quad (4-23)$$

である。

図 11: 回路浮遊成分があるときの回路図

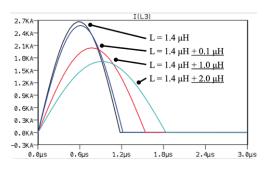

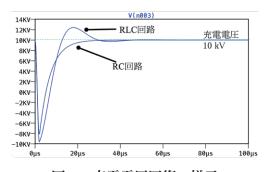

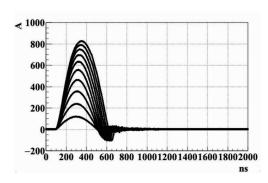

図 12 は浮遊インダクタンスを  $0.1~\mu$ H、  $1.0~\mu$ H、  $2.0~\mu$ H と変化させた際の出力電流波形 の違いを示したものである。シミュレーションは LTSpice [4] を用いて実行しており、印加電 圧は 10~kV、浮遊インダクタンスがない理想的 な場合におけるピーク電流は 2.7~kA である。図 から分かるように、浮遊インダクタンスが大き くなると、パルス幅は拡大し、ピーク電流は低下する。この現象は、インダクタンスが増加すると負荷に印加される有効電圧が低下し、結果として十分な電流を流せなくなることに起因する。ピーク電流の低下に対しては、回路耐圧設計に十分余裕がある場合には印加電圧を高める

ことで一定の補償が可能である。しかしながら、パルス幅の拡大は一度構成した回路では容易に変更できず、短パルスを必要とする電源の場合には大きな障害となる。浮遊インダクタンスは電源回路のループのみならず、キッカー電磁石との接続ケーブルなど、回路外部にも存在する。そのため、配線配置や部品間距離、接続構造などを十分に考慮し、実環境に即した回路設計を行うことが不可欠である。

図 12: 浮遊インダクタンスによる影響

図 13 は、回路の寄生抵抗 R を変化させた際の出力電流波形である。寄生抵抗の変化においては、減衰項の影響によりピーク電流が低下して、電流波形も理想的な LC 共振による正弦半波波形から外れ、尾を引くような形状へと変化していくことが確認できる。通常の構成では寄生抵抗値は小さく、ピーク電流やパルス形状に与える影響は限定的であるため、深刻な問題にはなりにくい。しかしながら、パルス幅が100 ns 程度の高速パルス電源の場合、表皮効果の影響も大きくなるため導体構造の選定には注意を要する。また逆にパルス幅が100  $\mu$ s と長い場合には減衰項の次定数  $\alpha$  との関係次第では影響が無視できなくなることもある。

## 4.4 充電部の回路動作

これまでにパルサー部における回路動作について定量的に考察してきたが、本節ではパルス電源のもう一つの構成要素である充電部の基本動作について述べる。簡単なケースとして、図8に示すような構成を考える。

まずスイッチがオフの状態では、充電部は高 圧 DC 電源、充電抵抗 R、および充放電用コンデ

図 13: 寄生抵抗による影響

ンサCから成る RC 回路として動作する。このとき、コンデンサ電圧はV(t) は時定数  $\tau=RC$  に従って充電される。ここで重要なのは、充電抵抗におけるジュール発熱である。RC 回路において、抵抗に消費されるエネルギーは全体の供給エネルギー  $E=\frac{1}{2}CV^2$  に等しい。したがって、繰り返し周波数 f で動作する場合、発熱量P は以下のようになる。

$$P = \frac{1}{2}CV^2f$$

(4-24)

注目すべき点は、発熱量は充電抵抗の値 R には 依存しないということである。充電抵抗を配置 しないような回路構成であっても、ケーブルな どがもつ有限の抵抗値で熱が消費されることに なる。繰り返しが低い場合にはほとんど発熱は 問題にならないが、意図しない箇所で発熱する 事象を引き起こしかねないので注意を要する。

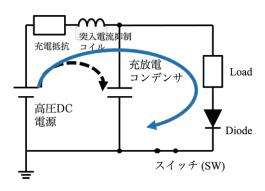

次に、SW がオンされたときの充電部の挙動 を考える。この状態では充電部も放電ループの 一部となり、抵抗 R がそのまま負荷 L と直列 に接続された RL 回路を形成することになる。 この構成では、瞬間的に大きな電流が流れ、ス イッチ素子に過大な負荷を与えるおそれがある。 このような電流の急峻な立ち上がりを抑制する ために、図 14 に示すように、充電部にリアク トルを挿入することがある。挿入するリアクト ルのインダクタンス値を、負荷インダクタンス  $L_{load}$  よりも十分に大きく取ることで、SW オン 時に RL 回路に流れる電流を抑制する。このよ うな構成により、スイッチ動作時の過渡現象を 制御できるが、RLC 回路として振る舞うことに なるため、図15に示すように条件によっては過 電圧が発生する可能性がある。この過電圧は充 電電圧を一時的に超過する可能性があり、コンデンサやスイッチ素子の耐電圧を超えると破壊の原因となる。こうした場合、充電部に環流ダイオードを用いることで過電圧を防止することも検討される(図 16)。

図 14: 充電部スイッチオン時の回路動作

図 15: 充電電圧回復の様子

図 16: 充電部の過電圧保護

#### 4.5 回路パラメータの設定

これまでの議論を踏まえることで、電源回路 に必要なパラメータを概算的に決定できる。

まず、入射用キッカー電磁石のように、必要 とされる蹴り角は数 mrad と比較的小さい一方 で、パルス幅が μs オーダーで求められる場合に ついて考える。3.3 節で取り上げた例に基づい て計算したキッカーパルス電源の代表的な定格 値を表1に示す。計算には、4.3節で導出した 集中定数回路モデルを用いている。また、浮遊 インダクタンスが 1 μΗ 存在する場合の設計値 も併記している。4.3 節で示した通り、浮遊イ ンダクタンスがあるとパルス幅が広がる。さら に、式(4-9)に示されるように、インダクタンス L が増加した場合にパルス幅とピーク電流を一 定に保つには、より高い電圧の印加が必要とな る。表の例では、必要電圧は 15 kV から 25 kV に上昇しており、浮遊インダクタンスが耐電圧 設計に大きな影響を及ぼすことがわかる。

表 1: 入射キッカーパルス電源の定格設計例

| パラメータ     | 定格 1                | 定格 2                |

|-----------|---------------------|---------------------|

| ピーク電流     | 4000 A              | 4000 A              |

| 負荷インダクタンス | $1.4~\mu\mathrm{H}$ | $1.4~\mu\mathrm{H}$ |

| 浮遊インダクタンス | $0~\mu\mathrm{H}$   | $1~\mu\mathrm{H}$   |

| パルス幅      | $1.2~\mu\mathrm{s}$ | $1.2~\mu\mathrm{s}$ |

| 充放電コンデンサ  | 100 nF              | 60 nF               |

| 印加電圧      | $15~\mathrm{kV}$    | $25~\mathrm{kV}$    |

次に、セプタム電磁石のように、必要とされる蹴り角は 100~mrad 程度と大きいが、許容されるパルス幅は  $100~\mu\text{s}$  オーダーと長い場合を考える。このようなケースにおける代表的な設計値を表 2~に示す。こちらも同様に、浮遊インダクタンスの影響を含めた定格値を併記している。セプタム電源の場合、十分に長いパルス幅が許容されるため、コンデンサ容量も大きく取ることができる。その結果式  $(4-9)~\text{からも明らかなように、必要な印加電圧は比較的小さく抑える$

ことができ、キッカー電磁石電源と比較すると 耐電圧設計上は裕度がある。

表 2: セプタム電磁石電源の定格設計例

| パラメータ     | 定格 1                 | 定格 2                 |

|-----------|----------------------|----------------------|

| ピーク電流     | 6000 A               | 6000 A               |

| 負荷インダクタンス | $3.7~\mu\mathrm{H}$  | $3.7~\mu\mathrm{H}$  |

| 浮遊インダクタンス | $0~\mu\mathrm{H}$    | $1~\mu\mathrm{H}$    |

| パルス幅      | $100~\mu \mathrm{s}$ | $100~\mu \mathrm{s}$ |

| 充放電コンデンサ  | $270~\mu\mathrm{F}$  | $220~\mu\mathrm{F}$  |

| 印加電圧      | 700 V                | 880 V                |

#### 4.6 スナバ回路によるノイズの抑制

本章の最後にパルス電源の回路でよく使われるノイズ吸収回路について紹介する。

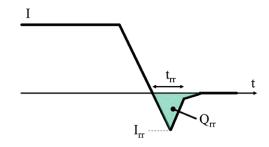

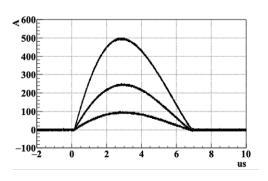

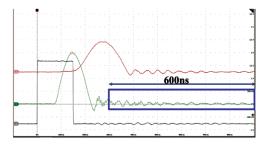

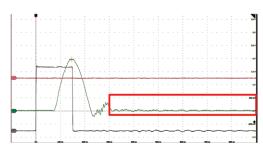

パルス電源の設計においては、整流用ダイ オードの過渡応答に起因するリンギングノイズ が重要な課題となる。このノイズは、ダイオー ドに逆方向電圧が印加された際、順方向に蓄積 されたキャリアが完全に除去されるまでの間に 逆方向電流が流れる逆回復時間に起因する。 図 17 にそのリカバリー波形の概要を示す。こ の現象においては、蓄積キャリア量が同一であ れば、パルス幅が短く波形の変化が急峻(すな わち di/dt が大きい) な場合ほど、流れる逆電流  $I_{rr}$  は大きくなる傾向がある。図 18、図 19 に波 形の実例を示す。これは、同一種類のダイオー ドを用いてコンデンサ容量を変更し、パルス幅 の違いによる影響を比較した結果である。図 18 はパルス幅が長い場合、図19は短い場合を示し ており、短パルス時により顕著な逆電流が観測 されている。図 3 に示したように、こうしたノ イズは入射ビームに悪影響を及ぼす可能性があ るため、発生したリンギングは迅速にダンピン グさせる必要がある。

これらの過渡応答を抑制するために、スナバ回路(snubber circuit)と呼ばれるノイズ吸収回路がしばしば用いられる。スナバ回路は一般に、RC をノイズ源に並列接続した構成をとる。図 20 にその基本構成を示す。 スナバ回路

図 17: ダイオードの逆回復波形

では、高周波成分がスナバコンデンサ  $C_S$  に流れ、スナバ抵抗  $R_S$  においてジュール熱として消費される。コンデンサの容量が大きいほど吸収できるエネルギーは大きくなるが、スナバ回路の効果を十分に発揮させるためには、スナバ回路の RC 時定数  $\tau=R_SC_S$  がターゲットとするノイズの振動数の時間スケール  $T_{\rm noise}$  よりも十分小さくなるように設計する必要がある  $(R_SC_S \ll T_{\rm noise})$ 。これにより、高周波成分がスナバ回路側に選択的に流れるようにすることができる。

図 21、図 22 に、スナバ回路の調整前後における波形を示す。調整前には明瞭なリンギングが確認されるが、*RC* 定数を適切に選定することで、このリンギングが大きく低減されていることがわかる。

以上のようにスナバ回路はパルス電源回路のノイズ吸収において重要な役割を果たす。スナバ素子の選定においてはダイオードの特性などを事前に把握しておけば、ある程度設計段階で行うことが可能である。しかし、過渡特性やノイズの振る舞いを完全に予測することは困難であるため、実機では後からパラメータ調整可能とする設計配慮が求められる。スナバ回路についてもう少し詳細を知りたい場合には[5]のノートなどが参考になる。

# 5 スイッチ部の進化と半導体スイッチ

前章ではパルス電源回路におけるスイッチ部が理想的に動作する場合の機構を述べた。本章では、パルス電源の心臓部とも言えるスイッチ部について、特に現在主流となりつつある半導

図 18: パルス幅が長い場合

図 19: パルス幅が短い場合

図 20: スナバ回路の構成

体スイッチについてその役割を概説する。

# **5.1** 高電圧・大電流スイッチとその候補デバイス概要

高電圧・大電流のパルス電源を構成するうえで、スイッチング素子(スイッチ部)は最も重要な要素の一つである。加速器用の入射パルス電源ではこれまで述べてきたように、高電圧・大電流・高速スイッチングという厳しい要件が課される。そのため加速器用パルス電源のスイッチ素子候補は限られており、ガス放電管であるサイラトロン(図 23 左)や半導体スイッチである MOSFET(図 23 右) や IGBT な

図 21: スナバ回路パラメータ調整前

図 22: スナバ回路パラメータ調整後

どである。ちなみに MOSFET は Metal-Oxside Semiconductor Field Effect Transistor、IGBT は Insulated Gate Bipolar Transistor の略である。これらの候補について、電圧電流定格、スイッチターンオン速度、高繰り返し性能についての簡易的な比較を表 3 に示す。

表 3: 高電圧・大電流スイッチ候補デバイスの 比較

|       | サイラトロン          | MOSFET | IGBT      |

|-------|-----------------|--------|-----------|

| 電圧定格  | 数十kV            | 1 kV   | 数 kV      |

| 電流定格  | 数十kA            | 100 A  | 数 kA      |

| ターンオン | 数十 ns           | 数十ns   | 数 $\mu$ s |

| 繰り返し数 | $< 100~{ m Hz}$ | MHz    | kHz       |

サイラトロンは、主に水素を封入した制御可能なガス放電管である。制御電極(グリッド)にトリガ信号を印加することで絶縁破壊を誘起し、大電流アーク放電が開始される。この放電が持続することで大電流を導通するスイッチとなる。数十kV/数kA級の電力に対応し、立ち上がり時間が数十nsと高速であることが大きな利点である。

ただし、次のような欠点も挙げられる。数万 ~十万ショットでの性能が劣化し、加速器の運 用では 5-10 年おきに交換が必要となる。また、 ジッターが 10 ns 程度と小さくないうえ、ガス 圧の変動によってジッター量が変化する。構造 的にもデバイス自体が大きく、ヒーターが必要 であることから回路全体が大型化しやすい。さ らに近年の課題として、世界的に製造できる企 業が数社しかなく、入手性が良くないという問題がある。これらデメリットは半導体スイッチ にはない。半永久的な使用が可能であり、ジッターレスで、固体デバイスであるために小型化 が可能である。また、商用入手性も高く、流通 面でも優位性がある。

サイラトロンは依然として高電圧・大電流に 最適なデバイスであり、現在でも多くの加速器 パルス電源で使用されている。しかし、近年半 導体デバイスの電圧電流定格が向上してきたこ とにより、半導体スイッチが高電圧・大電流ス イッチとして急速に普及しつつある。半導体パ ルス電源を用いた開発などは過去の OHO [6,7] や半導体メーカーの記事 [8] などにも記載があ るので、興味がある方は参考にされたい。

# 5.2 SiC パワー半導体デバイスとその構造

加速器用パルス電源のスイッチには、MOSFET や IGBT などのパワー半導体素子の導入が進んでいる。本節では、スイッチ半導体化の立役者である SiC パワーデバイスについてと半導体スイッチの構造について概説する。

従来のパワー半導体は、Si(シリコン)ウェハを基板として長年にわたり研究開発が進められてきた。その結果、Si デバイスの性能は物性限界に近づいていたが、サイラトロンのような高電圧・大電流スイッチを完全に代替するには至っていなかった。この限界を突破する手段として、近年では SiC(シリコンカーバイド)や GaN(窒化ガリウム)といったワイドバンドギャップ材料によるデバイス開発が急速に進んでいる。SiC は Si に比べてバンドギャップが約3倍、絶縁破壊電界が約10倍と大きく、理論的にはデバイス性能は最大300倍に達する。同じ

図 23: 左図サイラトロン (e2v; CX1175C [10]) と 右図 MOSFET (Rohm; SCT3040KL [11])。図の MOSFET はディスクリートタイプになってい て、実際のチップはさらに小さい。

耐圧条件であれば、より高電力密度かつ高速スイッチングが可能であり、次世代パワーデバイスとして期待されている [9]。

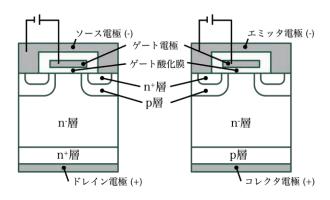

図 24 に、パワー半導体である MOSFET と IGBT の基本構造を示す。MOSFET は npn の 3 層構造で、ゲート電圧により p 層にチャネル と呼ばれる電流が流れる状態を形成し、ドレイ ン - ソース間に電流を流すことができるように なる。ゲート電圧を遮断するとチャネルは消滅 し、電流も遮断される。IGBT は pnpn の 4 層構 造をもち、MOS 制御によってコレクターエミッ タ間の電流をオン/オフする。両者はともに電 圧制御型スイッチであるが、MOSFET はユニ ポーラ素子で蓄積キャリアを持たないため高速 動作が可能である。ただし、耐圧を上げるには  $n^-$  ドリフト層を厚くする必要があり、オン抵 抗が増加する傾向がある。一方、IGBT はバイ ポーラ素子で蓄積キャリアを伴うためスイッチ ング速度はやや劣るが、高耐圧化しても低オン 抵抗を維持できる。

このため、MOSFET は高速スイッチング用途

に、IGBT は高耐圧用途に適しており、用途に 応じて使い分けられている。また MOSFET も SiC 化したことで耐圧は上がっており、IGBT の 代用としても使用されるようになっている。

図 24: MOSFET(左) と IGBT(右) の基本構造

# 5.3 半導体スイッチの基本動作

本節では半導体スイッチのスイッチ時の基本 動作について紹介する。

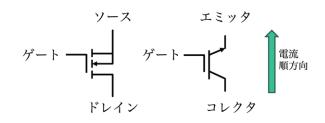

まず基本的な回路記号についてであるが、 MOSFET と IGBT については図 25 のように表 される。電流の流れる順方向の向きは図の矢印 の向きである。

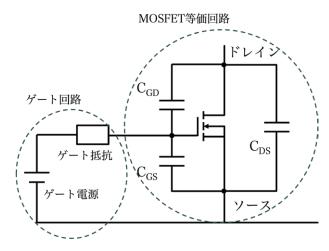

次に、MOSFET を例にスイッチ動作を説明する。等価回路は 図 26 に示す通りであり、ゲート、ドレイン、ソース間にはそれぞれ無視できない寄生容量が存在する(特にゲート/ソース間には 1 nF 程度の容量がある)。これらの容量はスイッチング特性に大きく影響を与える。

図 27 は、MOSFET のターンオン時の電流、電圧特性を示したものである。ゲートに電圧を印加すると、まず寄生容量の充電が始まり、ゲート電圧はただちには上昇せず、動作は数段階を経て進行する。この間、電圧と電流が同時にゼロでない領域では、その積に相当するスイッチング損失(IV 損失)が発生し、素子に熱が生じる。したがって、切り替え時間の短縮は高効率化に直結する。スイッチング速度を高める手法として、ゲート抵抗 (R) を小さくすることが挙げられる。例えば  $R=10~\Omega$ ,容量  $C=1~\mathrm{nF}$  とすると、時定数  $RC=10~\mathrm{nS}$  に従ってスイッチング

が進行する。ゲート抵抗を小さくすれば速度は 向上するが、ノイズ耐性が低下し、外部ノイズ による誤点弧が生じやすくなる。加速器応用で は誤点弧が重大故障につながるため、ゲート抵 抗値の選定には慎重な設計判断が求められる。

ターンオフ動作においても寄生容量の放電が 必要であり、ゲート電圧は急には下がらない。 ターンオンとは逆のプロセスをたどり、スイッ チは段階的にオフ状態へと移行する。

図 25: MOSFET(左) と IGBT(右) の回路記号

図 26: MOSFET 等価回路

## 5.4 設計時の注意事項

本節では、半導体スイッチを設計・構成する際の注意点について述べる。

# 5.4.1 素子の電圧・電流定格

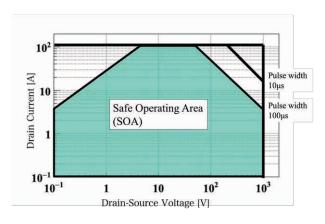

スイッチ素子の定格は、データシートに記載されている Safe Operating Area(SOA)を参照する必要がある。SOA は、図 28 に示すように、電圧および電流の動作限界を示した領域である。

図 27: MOSFET ターンオン特性。上図はゲート 電圧の変化を示し、下図はドレイン-ソース間の 電流、電圧の変化を示している。

この中には、絶対最大定格のほか、熱制限による領域(図の右上)や、素子のオン抵抗に起因する電力制限領域(図の左上)などが含まれる。

要求される電圧または電流が単一素子の定格を超える場合は、素子を直列または並列に接続して対応する。素子直並列時の設計上の注意点については、次節で述べる。

図 28: Safe Operating Area (SOA) の例

# 5.4.2 素子の直列接続時の保護

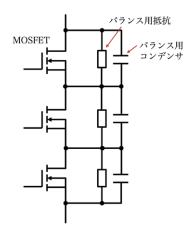

複数のスイッチ素子を直列接続する場合、各素子にかかる電圧を均等に保つ必要がある。そうしないと一部の素子に過電圧が印加され、破壊の原因となる。図 29 に、直列接続時の代表的な保護構成を示す。

まず静的な電圧バランスについてである。各 素子にはわずかながら漏れ電流が存在するが、 その大きさは個体差が大きく、内部抵抗が高い 素子ほどばらつきが生じやすい。このばらつき によって電圧分担が不均等となるのを防ぐため、 素子ごとに並列にバランス抵抗を接続する。抵 抗値は、データシートに記載された漏れ電流 や実測をもとに設定する必要がある。動的(ス イッチング中)のバランスについても同様の考 えで素子を並列に追加する。ただし、動的な電 圧分担は個体の寄生容量の差で決まる。そこで 各素子に並列にコンデンサを追加する。こちら もデータシート記載の寄生容量や実測をもとに 値を決定する。

動的な電圧バランスについて、ターンオン時に一部の素子が他よりも早くスイッチングすると、導通のタイミングが揃わず、他の素子に一時的な過電圧が加わる可能性がある。これを防ぐには、すべての素子のターンオン速度を揃えることが重要であり、ゲート抵抗を緻密に調整する必要がある。ただし調整には限界があるため、事前にすべての素子の閾値電圧を測定し、特性が揃った素子を選別して基板に搭載するなどの工夫が求められる。

#### 5.4.3 素子の並列接続時

MOSFET などの半導体素子を並列接続する場合、基本的には素子個体差による電流バラツキの影響は大きくない。特に MOSFET には、温度上昇とともに内部抵抗が増加するという特性がある。このため、一時的に電流が多く流れる素子が加熱によってオン抵抗を増加させ、結果として電流が他の素子に分散されるという正のフィードバック機構が働く。この自己平衡作用により、ある程度の電流バランスが自然に保たれる。

図 29: 素子直列接続時

一方で、実際の回路では素子間の電流バランスに大きく影響するのは、素子そのものよりも伝送線路側のバランスである場合が多い。特に短パルス用の回路では線路の自己インダクタンスや相互インダクタンスの影響が大きくなる。これにより電流分担に不均衡が生じやすくなる。そのため、配線の物理的配置を工夫し、ループ面積を極力小さくする、あるいは円形配置などによりインダクタンスバランスを取るといった対策が必要となる。

#### 5.4.4 ゲート回路

ゲート回路の設計においては、電気的絶縁を確保することが重要である。特に、ゲートドライバに供給される信号や電源は、スイッチ素子の主回路とは電位が異なるため、絶縁して供給する必要がある。

パルス電源では、高電圧印加のためにスイッチ素子を直列接続する構成が一般的であり、その際に中点を接地することができない。このため、各素子のゲート駆動には絶縁型のゲート信号および絶縁電源を用いなければならない。ゲート信号の絶縁には、光ファイバ絶縁やフォトカプラによる絶縁、トランスを用いた絶縁方法などがある。ゲート電源の供給には、一般的に絶縁型 DC/DC コンバータが用いられる。これにより、各スイッチ素子の電位に応じた独立した電源を確保し、主回路と安全に切り離された状態でゲート駆動が可能となる。

# 6 半導体パルス電源開発例

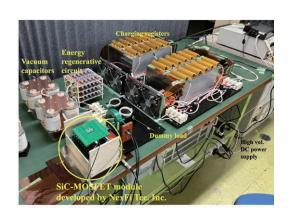

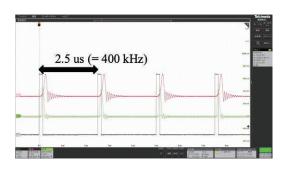

最後にこれまで紹介した半導体パルス電源 について開発例を簡単に紹介する。図 30 は、 KEK-PF で現在開発中の半導体パルス電源であ る。本電源は、PF において時間的に孤立させた 大電荷シングルバンチの軌道を一時的に変化さ せるためのキッカーシステムに用いられるもの である。要求される仕様は、高電圧(15 kV)、 大電流 (500A)、短パルス (200 ns 幅)、高繰り 返し(800 kHz)という、非常に厳しい条件を 満たす必要がある。これらの要求は従来のサイ ラトロンでは実現が困難であり、大電流と高速 動作を両立可能な SiC-MOSFET 半導体スイッ チを用いた新たなパルス電源として開発が進め られている。本電源は集中定数型で構成されて おり、パラメータを調整することで入射用キッ カーパルス電源への応用も容易である。入射用 途に応用する場合には、繰り返し要求(10 Hz 程 度) であるので本電源は十分なマージンをもっ て運転できる。これにより、サイラトロンに見 られる駆動回数による劣化や、それに起因する メンテナンス性の課題を回避できる点が大きな 利点となる。

図 30: 半導体パルス電源試験機

図 30 に示しているスイッチングモジュールは (株) NexFi テクノロジー [12] により特注で開発されたもので、 $15~\rm cm$  立方程度の大きさで耐電圧  $24~\rm kV$ 、 $400~\rm kHz$  でのスイッチングが可能である。図に示しているようにテーブル上に載る程度にコンパクトにまとめられたパルス電源

では、エネルギー回収機能も備えており、最大で400kHzの電流出力を実現している(図 31)。また100 kHzで2か月間にわたる長期運転試験を実施した結果、電流安定度は0.14%以上、スイッチ動作回数は4200億回を超えるなど、十分な信頼性が確認されている[13]。本電源はまだ開発途中のものであり、興味のある方は今後の報告を期待されたい。

図 31: 試験機出力の様子

# 7 まとめ

本稿では電子蓄積リングで用いるパルス電源について概説した。2章では電子ビームを入射するにあたり、その入射方法とパルス電磁石が必要な理由を述べた。3章ではそのパルス電磁石に必要な電流量を必要な蹴り角と磁石の構造から概算し、パルス電源にはkA級の電流を流すことが必要と述べた。4章では集中定数型の電源回路を例に出力波形を定量的に解説し、パルス電源に必要なパラメータ例を紹介した。5章ではパルス電源の中核であるスイッチイングデバイスについて、パワー半導体であるMOSFETを中心に、その構造、動作原理、駆動方法、および設計における留意点を述べ、最後に6章で開発中のパルス電源について紹介した。

以上のようにパルス電源の設計の際に必要なパラメータの規模や注意すべきこと、選ぶべきスイッチングデバイスなどを筆者の経験も交えた具体例とともに紹介した。冒頭にも述べたように実際に設計する際には多くの検討課題が存在するが、本稿で得られた知識で少なくとも、パルス電源の初期設計の際に進むべき方向に見通しを得られるようになれば幸いである。また

電源としては特殊用途であるパルス電源にも興味をもつようになって頂ければなお幸いである。

# 8 謝辞

加速器におけるパルス電源開発では、KEK内 外含めて多くの方のご協力頂いて進むことがで きております。特に加速器六系の満田史織氏と 内藤大地氏には筆者がパルス電源開発を進める きっかけと強力なご助言を常に頂いており、深 く感謝いたします。加速器六系の皆様にも多大 なご心配とご協力を頂き大変感謝しております。 また、本稿で紹介させて頂いた知識や考え方は 開発中の半導体パルス電源の開発時に得た知識 がもとになっています。半導体パルス電源開発 におきましては、SiC スイッチングモジュール を用いた半導体パルス電源の開発にあたり多大 なご協力とご助言を頂きました株式会社 NexFi テクノロジーの方々、開発中の半導体パルス電 源の充電部やダイオードバンクの製作にあたり ご協力を頂きました株式会社東京電子の方々、 高精度の高圧 DC 電源を開発して頂きました有 限会社 HSE の方々に感謝申し上げます。最後 に、パルス電源についての講義の機会をくださ いました OHO' 25 の関係者の皆さまに心から 深く感謝いたします。

## 参考文献

- [1] 佐藤政則, "KEK 電子・陽電子入射器による 5 リング同時トップアップ入射", 加速器学会誌 Vol. 17, No. 3, 2020(169–173)

- [2] 中山久義, "ビーム輸送の基礎 ビーム光学 と電磁石の基礎", OHO2009

- [3] C. S. Fann, H. P. Chang, C. L. Chen, Y. S. Cheng, K. T. Hsu, S. Y. Hsu, K. K. Lin, K. L. Tsai, C.Y. Wu, "IM-PLEMENTATION OF USING IGBT SWITCH BASED PULSER FOR TPS BOOSTER EXTRACTION KICKER", IPAC2021, doi:10.18429/JACoW-IPAC2021-MOPAB082

- [4] Analog Devices, https://www.analog.

- [5] Rohm, https://fscdn.rohm.com/

jp/products/databook/applinote/

discrete/sic/mosfet/sic-mos\_

snubber\_circuit\_design\_an-j.pdf

- [6] 高柳智弘, "パルス電磁石電源", OHO2018

- [7] 高柳智弘, "大電力半導体スイッチ", OHO2024

- [8] Rohm, https://www.rohm.co.jp/electronics-basics/sic/sic\_what1

- [9] 谷内利明, 松本寿彰, 小倉常雄, 小谷和也, 田井 裕通, 竹内 宏行, "実践パワーエレク トロニクス入門 パワー半導体デバイス", オーム社

- [10] CX1175C データシート, https: //www.teledyne-e2v.com/en-us/ Solutions\_/Documents/datasheets/ Thyratron/cx1175c.pdf

- [11] SCT3040KL  $\vec{\mathcal{T}} \beta \triangleright \uparrow$ , Rohm, https://fscdn.rohm.com/en/products/databook/datasheet/discrete/sic/mosfet/sct3040kl-e.pdf

- [12] Nexfi technology inc., https://www.nexfi-tech.com

- [13] S. Shinohara, et. al., "Development of a Prototype Pulsed Power Supply using SiC-MOSFETs for a Fast Kicker System in KEK-PF", in Proc. IPAC' 23, Venice, Italy, May 2023, pp. 4366–4368. doi:10.18429/JACoW-IPAC2023-THPA168